Intel says it will stuff one trillion transistors into a package by 2030

Last year, Intel said that it would take process leadership away from TSMC and Samsung Foundry by 2025. Right now, TSMC and Samsung are the top two chip foundries in the world both shipping the most cutting-edge chips. Next year, both will be delivering chips manufactured using the 3nm process node. Let's make this as simple as possible. The smaller the process node, the smaller the transistors used to power a chip which means more of them can be shoehorned inside.

Typically, the higher a chip's transistor count, the more powerful and energy-efficient it is

Typically, the more transistors inside a chip, the more powerful and energy-efficient it is. Let's use the iPhone as an example. The A13 Bionic SoC released in 2013 was used on the iPhone 11 series and was made using TSMC's 7nm process node. The chip contained 8.5 billion transistors. The A16 Bionic that powers the iPhone 14 Pro and iPhone 14 Pro Max is made using TSMC's 4nm process node (technically an enhanced 5nm process) and sports close to 16 billion transistors.

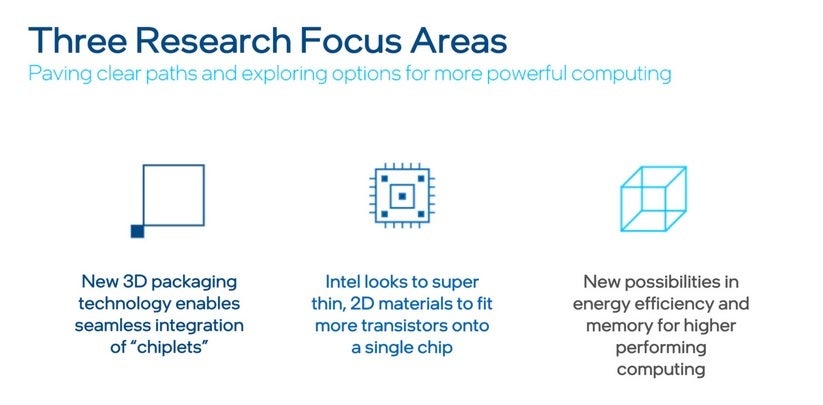

Three areas of research that Intel will focus on

By 2025 we could see TSMC and Samsung pushing out 2nm chips with the latter already talking about producing 1.4nm chips by 2027. TSMC has mentioned 1nm chips but hasn't given a time frame for their arrival. But Intel can't be dismissed and at IEDM 2022 (International Electron Devices Meeting), the company celebrated the 75th anniversary of the creation of the transistor by announcing plans to get one trillion transistors on a package by 2030.

A package is the housing that chips are placed in. They are either soldered to a printed circuit board (PCB) or plugged into the PCB. One chip die is found inside a package unless it is a Multi-Chip Module. An example of this would be an eMMC flash card which contains flash memory and a flash memory controller.

Intel says that it will be able to keep Moore's Law alive; this is the observation made by Intel co-founder Gordon Moore that originally called for the transistor count in chips to double every year. Moore revised this 10 years later as he looked for transistor counts to double every other year by 1975. Intel will be helped by having the first crack at the High Numerical Aperture Extreme Ultraviolet Lithography machine, the next-generation lithography machine designed to etch thin circuitry patterns on the wafers that become chips.

How Intel plans on regaining process leadership

The new machines will allow foundries to etch circuitry designs at higher resolutions to enable 1.7x smaller chip features and 2.9x increased chip density. Each machine carries a price tag in the neighborhood of $300 million. Gary Patton, Intel vice president, and general manager of Components Research and Design Enablement, said, "Seventy-five years since the invention of the transistor, innovation driving Moore’s Law continues to address the world’s exponentially increasing demand for computing."

Patton continued, "At IEDM 2022, Intel is showcasing both the forward-thinking and concrete research advancements needed to break through current and future barriers, deliver to this insatiable demand, and keep Moore’s Law alive and well for years to come."

One of the most important discoveries in the industry is the replacement of FinFET transistors with Gate-All-Around (GAA). Unlike FinFET (which TSMC is still using for its 3nm process node), current flows can be manipulated on all four sides of the channel and will use vertically stacked nanoribbons. Samsung is using GAA for its 3nm chips while TSMC won't follow suit until it starts producing 2nm chips in a few years. Intel, which calls its GAA tech RibbonFET, will start shipping such chips in 2024.

Also helping Intel toward its goal of producing packages with one trillion transistors are new innovations in the packaging of chips with a 10x improvement in density. This will allow a huge increase in the number of transistors that can fit inside a small area. And new materials to help produce smaller transistors include the use of a super-thin material that is comprised of just three atoms!

Things that are NOT allowed: